讲一下实际在做的工作中遇到的电阻的功能

有尺寸、阻值、精度和功率。电阻的应用场景非常多,都是围绕着电阻的特性来使用的。我们重点讲一下实际在做的工作中遇到的电阻的功能,理论知识和计算公式就不赘述了。

在初学者心目中,电阻就是拿来分压用的,但是实际项目中,绝大部分电阻都不是当作分压用的。

我们统计过,一个平台的硬件电路中,大约20%的电阻是做上拉下拉使用,30%的电阻做EMCESD使用,40%的电阻占位置和跳线%的电阻用来做电压采样,剩下的最多只有两三颗是用来做正经的分压用途。

上拉,就是把电路拉高到电源,下拉,就是把电路拉高到地。下面有几张参考图。

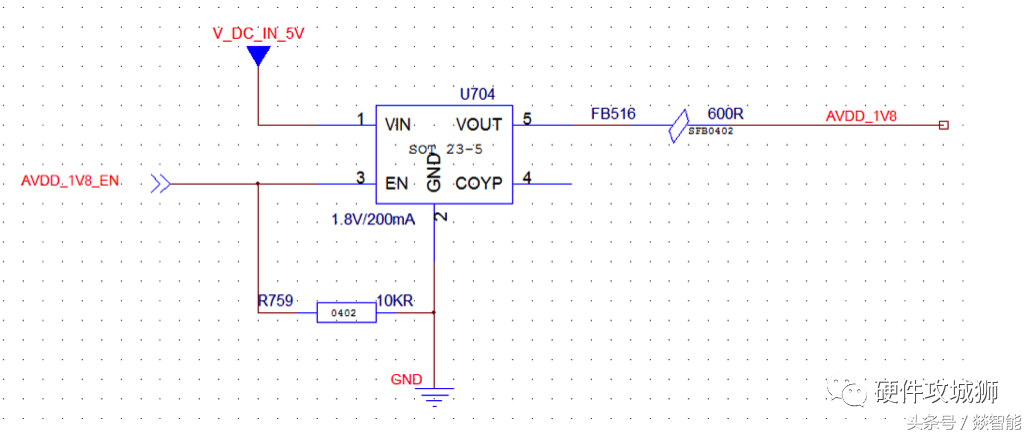

↑NMOS开关控制脚的下拉电阻,R732。使MOS管在无控状态下保持关闭。

上下拉的最大的作用,一是让线路在无人控制的情况下维持在固定的状态,二是提升驱动能力。

关于无人控制,很多人会认为,系统开机之后,我配置了这个GPIO口,就能控制了呀,为什么存在无人控制的情况呢?

对,开机之后都能控制,但是系统刚上电,未开机,或者开机过程中,GPIO口却都是在无控状态。如果只供电但还没有开机,电源的控制脚是一个默认内部上拉的GPIO口,电源就被打开了,经常导致电流灌进还没有运行起来的其他GPIO内,导致上电漏电。

如果开机,开机的过程一般是:上电-复位-电源初始化-跑引导程序-内核运行-应用运行,用户配置代码要么在内核中,要么在应用程序中,改不到引导程序的。虽然前面无控的时间很短,可能只有几百毫秒,但是有可能导致某些GPIO口的默认状态不对导致外部电源被意外打开,一样有可能出现漏电的情况。如果是灯的开关,就非常有可能在开机一瞬间灯亮一下,跑到程序设定的地方才会被关闭。

因此,对开关脚(EN,enable),选择GPIO的时候要选择默认是关闭状态的GPIO口,保险起见应当预留一个开关上下拉的电阻,用来确保开关脚的默认状态是对的。

这类开关上下拉电阻,通常用于电源芯片的开关、灯的开关、模拟开关等控制脚上。

这种用法也会用在中断信号上,通过外加一个上拉电阻,使中断脚在没有输出的情况下保持高电平,一旦输出低电平,就会被拉下来。反之亦然。

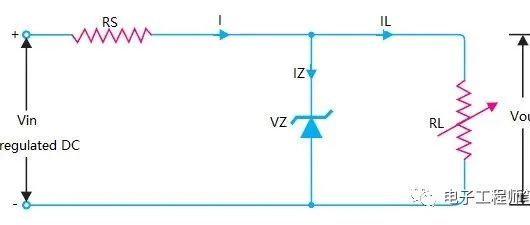

这些上下拉电阻,通常在10KR-100KR之间,电阻小了会导致漏电大或者GPIO控制不了,电阻大了会导致和芯片内部上下拉冲突。GPIO输出电阻一般在10kR以下,内部上下拉一般在100KR上下。(实际上也是两个电阻分压的原理)

至于I2C的上拉,是协议要求的。I2C两根线要求默认是高电平,一旦被拉到低电平就会认为有数据要发送了。在I2C主机和从机都没有控制的情况下,需要维持在高电平。而I2C硬件上都是OC门,没办法自己上拉,因此就需要外部上拉电阻。这种情况算是个特例。

SDIO接口,就是接SD卡、TF卡的接口,增加10KR-33KR的上拉电阻有助于提高驱动能力。某些小厂生产的比较水的SD卡和TF卡,会不容易被识别到,增加上拉能够减小不读卡的概率。

文章出处:【微信号:mcu168,微信公众号:硬件攻城狮】欢迎添加关注!文章转载请注明出处。

常用的版本控制管理系统有:Git(分布式版本控制管理系统)与SVN(集中式版本控制管理系统)。 本次分享Git在

常用的版本控制管理系统有:Git(分布式版本控制管理系统)与SVN(集中式版本控制管理系统)。

的使用方法 /

试制后,非常有可能发生从电路图无法预测的瞬态现象、超乎预期的波动、余量不足等问题。

的适用性确认和准备 /

是否适用的方法和步骤。 本篇介绍右侧流程图的②确认在绝对最大额定值范围内。

的晶体管适用性确认-确认在绝对最大额定值范围内 /

区)范围内 /

是否适用的方法和步骤。 本篇将介绍右侧流程图的④确认在使用环境和温度下降额的SOA范围内。

使用温度降额后的SOA范围内 /

是否适用的方法和步骤。 本文将介绍右侧流程图的“⑥确认平均功耗在额定功率范围内”。由于这

的晶体管适用性确认-确认平均功耗在额定功率范围内 /

是否适用的方法和步骤。 本文将对虽然右侧流程图中没有提及,但在下面项目中有的第⑦“确认芯片温度”进行说明。

的晶体管适用性确认-确认芯片温度 /

是否适用的方法和步骤。本文将进行最后的汇总。 前面按照右侧流程图及下列各项确认了所选晶体管在实

全球与中国电流检测贴片电阻市场决策建议及投资趋势预测报告2023-2030年

全球与中国电流检测贴片电阻市场决策建议及投资趋势预测报告2023-2030年